Moore's law

| Semiconductor device fabrication |

|---|

|

|

MOSFET scaling (process nodes) |

|

Future

|

| Futures studies |

|---|

| Concepts |

| Techniques |

| Technology assessment and forecasting |

| Related topics |

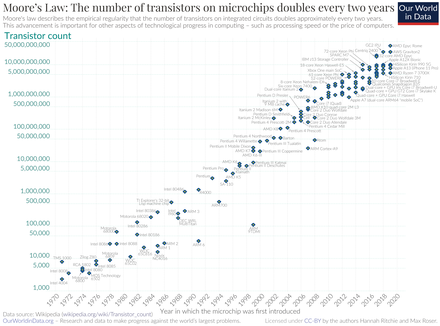

Moore's law is the observation that the number of transistors in an integrated circuit (IC) doubles about every two years. Moore's law is an observation and projection of a historical trend. Rather than a law of physics, it is an empirical relationship. It is an experience-curve law, a type of law quantifying efficiency gains from experience in production.

The observation is named after Gordon Moore, the co-founder of Fairchild Semiconductor and Intel (and former CEO of the latter), who in 1965 noted that the number of components per integrated circuit had been doubling every year,[a] and projected this rate of growth would continue for at least another decade. In 1975, looking forward to the next decade, he revised the forecast to doubling every two years, a compound annual growth rate (CAGR) of 41%. Moore's empirical evidence did not directly imply that the historical trend would continue, nevertheless his prediction has held since 1975 and has since become known as a "law".

Moore's prediction has been used in the semiconductor industry to guide long-term planning and to set targets for research and development, thus functioning to some extent as a self-fulfilling prophecy. Advancements in digital electronics, such as the reduction in quality-adjusted microprocessor prices, the increase in memory capacity (RAM and flash), the improvement of sensors, and even the number and size of pixels in digital cameras, are strongly linked to Moore's law. These ongoing changes in digital electronics have been a driving force of technological and social change, productivity, and economic growth.

Industry experts have not reached a consensus on exactly when Moore's law will cease to apply. Microprocessor architects report that semiconductor advancement has slowed industry-wide since around 2010, slightly below the pace predicted by Moore's law. In September 2022, Nvidia CEO Jensen Huang considered Moore's law dead,[2] while Intel CEO Pat Gelsinger was of the opposite view.[3]

History

[edit]In 1959, Douglas Engelbart studied the projected downscaling of integrated circuit (IC) size, publishing his results in the article "Microelectronics, and the Art of Similitude".[4][5][6] Engelbart presented his findings at the 1960 International Solid-State Circuits Conference, where Moore was present in the audience.[7]

In 1965, Gordon Moore, who at the time was working as the director of research and development at Fairchild Semiconductor, was asked to contribute to the thirty-fifth anniversary issue of Electronics magazine with a prediction on the future of the semiconductor components industry over the next ten years.[8] His response was a brief article entitled "Cramming more components onto integrated circuits".[1][9][b] Within his editorial, he speculated that by 1975 it would be possible to contain as many as 65000 components on a single quarter-square-inch (~ 1.6 cm2) semiconductor.

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year. Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years.[1]

Moore posited a log–linear relationship between device complexity (higher circuit density at reduced cost) and time.[12][13] In a 2015 interview, Moore noted of the 1965 article: "... I just did a wild extrapolation saying it's going to continue to double every year for the next 10 years."[14] One historian of the law cites Stigler's law of eponymy, to introduce the fact that the regular doubling of components was known to many working in the field.[13]

In 1974, Robert H. Dennard at IBM recognized the rapid MOSFET scaling technology and formulated what became known as Dennard scaling, which describes that as MOS transistors get smaller, their power density stays constant such that the power use remains in proportion with area.[15][16] Evidence from the semiconductor industry shows that this inverse relationship between power density and areal density broke down in the mid-2000s.[17]

At the 1975 IEEE International Electron Devices Meeting, Moore revised his forecast rate,[18][19] predicting semiconductor complexity would continue to double annually until about 1980, after which it would decrease to a rate of doubling approximately every two years.[19][20][21] He outlined several contributing factors for this exponential behavior:[12][13]

- The advent of metal–oxide–semiconductor (MOS) technology

- The exponential rate of increase in die sizes, coupled with a decrease in defective densities, with the result that semiconductor manufacturers could work with larger areas without losing reduction yields

- Finer minimum dimensions

- What Moore called "circuit and device cleverness"

Shortly after 1975, Caltech professor Carver Mead popularized the term "Moore's law".[22][23] Moore's law eventually came to be widely accepted as a goal for the semiconductor industry, and it was cited by competitive semiconductor manufacturers as they strove to increase processing power. Moore viewed his eponymous law as surprising and optimistic: "Moore's law is a violation of Murphy's law. Everything gets better and better."[24] The observation was even seen as a self-fulfilling prophecy.[25][26]

The doubling period is often misquoted as 18 months because of a separate prediction by Moore's colleague, Intel executive David House.[27] In 1975, House noted that Moore's revised law of doubling transistor count every 2 years in turn implied that computer chip performance would roughly double every 18 months[28] (with no increase in power consumption).[29] Mathematically, Moore's law predicted that transistor count would double every 2 years due to shrinking transistor dimensions and other improvements.[30] As a consequence of shrinking dimensions, Dennard scaling predicted that power consumption per unit area would remain constant. Combining these effects, David House deduced that computer chip performance would roughly double every 18 months. Also due to Dennard scaling, this increased performance would not be accompanied by increased power, i.e., the energy-efficiency of silicon-based computer chips roughly doubles every 18 months. Dennard scaling ended in the 2000s.[17] Koomey later showed that a similar rate of efficiency improvement predated silicon chips and Moore's law, for technologies such as vacuum tubes.

Microprocessor architects report that since around 2010, semiconductor advancement has slowed industry-wide below the pace predicted by Moore's law.[17] Brian Krzanich, the former CEO of Intel, cited Moore's 1975 revision as a precedent for the current deceleration, which results from technical challenges and is "a natural part of the history of Moore's law".[31][32][33] The rate of improvement in physical dimensions known as Dennard scaling also ended in the mid-2000s. As a result, much of the semiconductor industry has shifted its focus to the needs of major computing applications rather than semiconductor scaling.[25][34][17] Nevertheless, leading semiconductor manufacturers TSMC and Samsung Electronics have claimed to keep pace with Moore's law[35][36][37][38][39][40] with 10, 7, and 5 nm nodes in mass production.[35][36][41][42][43]

Moore's second law

[edit]As the cost of computer power to the consumer falls, the cost for producers to fulfill Moore's law follows an opposite trend: R&D, manufacturing, and test costs have increased steadily with each new generation of chips. The cost of the tools, principally EUVL (Extreme ultraviolet lithography), used to manufacture chips doubles every 4 years.[44] Rising manufacturing costs are an important consideration for the sustaining of Moore's law.[45] This led to the formulation of Moore's second law, also called Rock's law (named after Arthur Rock), which is that the capital cost of a semiconductor fabrication plant also increases exponentially over time.[46][47]

Major enabling factors

[edit]

Numerous innovations by scientists and engineers have sustained Moore's law since the beginning of the IC era. Some of the key innovations are listed below, as examples of breakthroughs that have advanced integrated circuit and semiconductor device fabrication technology, allowing transistor counts to grow by more than seven orders of magnitude in less than five decades.

- Integrated circuit (IC): The raison d'être for Moore's law. The germanium hybrid IC was invented by Jack Kilby at Texas Instruments in 1958,[48] followed by the invention of the silicon monolithic IC chip by Robert Noyce at Fairchild Semiconductor in 1959.[49]

- Complementary metal–oxide–semiconductor (CMOS): The CMOS process was invented by Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor in 1963.[50][51][52]

- Dynamic random-access memory (DRAM): DRAM was developed by Robert H. Dennard at IBM in 1967.[53]

- Chemically amplified photoresist: Invented by Hiroshi Ito, C. Grant Willson and J. M. J. Fréchet at IBM circa 1980,[54][55][56] which was 5–10 times more sensitive to ultraviolet light.[57] IBM introduced chemically amplified photoresist for DRAM production in the mid-1980s.[58][59]

- Deep UV excimer laser photolithography: Invented by Kanti Jain[60] at IBM circa 1980.[61][62][63] Prior to this, excimer lasers had been mainly used as research devices since their development in the 1970s.[64][65] From a broader scientific perspective, the invention of excimer laser lithography has been highlighted as one of the major milestones in the 50-year history of the laser.[66][67]

- Interconnect innovations: Interconnect innovations of the late 1990s, including chemical-mechanical polishing or chemical mechanical planarization (CMP), trench isolation, and copper interconnects—although not directly a factor in creating smaller transistors—have enabled improved wafer yield, additional layers of metal wires, closer spacing of devices, and lower electrical resistance.[68][69][70]

Computer industry technology road maps predicted in 2001 that Moore's law would continue for several generations of semiconductor chips.[71]

Recent trends

[edit]

One of the key technical challenges of engineering future nanoscale transistors is the design of gates. As device dimensions shrink, controlling the current flow in the thin channel becomes more difficult. Modern nanoscale transistors typically take the form of multi-gate MOSFETs, with the FinFET being the most common nanoscale transistor. The FinFET has gate dielectric on three sides of the channel. In comparison, the gate-all-around MOSFET (GAAFET) structure has even better gate control.

- A gate-all-around MOSFET (GAAFET) was first demonstrated in 1988, by a Toshiba research team led by Fujio Masuoka, who demonstrated a vertical nanowire GAAFET that he called a "surrounding gate transistor" (SGT).[72][73] Masuoka, best known as the inventor of flash memory, later left Toshiba and founded Unisantis Electronics in 2004 to research surrounding-gate technology along with Tohoku University.[74]

- In 2006, a team of Korean researchers from the Korea Advanced Institute of Science and Technology (KAIST) and the National Nano Fab Center developed a 3 nm transistor, the world's smallest nanoelectronic device at the time, based on FinFET technology.[75][76]

- In 2010, researchers at the Tyndall National Institute in Cork, Ireland announced a junctionless transistor. A control gate wrapped around a silicon nanowire can control the passage of electrons without the use of junctions or doping. They claim these may be produced at 10 nm scale using existing fabrication techniques.[77]

- In 2011, researchers at the University of Pittsburgh announced the development of a single-electron transistor, 1.5 nm in diameter, made out of oxide-based materials. Three "wires" converge on a central "island" that can house one or two electrons. Electrons tunnel from one wire to another through the island. Conditions on the third wire result in distinct conductive properties including the ability of the transistor to act as a solid state memory.[78] Nanowire transistors could spur the creation of microscopic computers.[79][80][81]

- In 2012, a research team at the University of New South Wales announced the development of the first working transistor consisting of a single atom placed precisely in a silicon crystal (not just picked from a large sample of random transistors).[82] Moore's law predicted this milestone to be reached for ICs in the lab by 2020.

- In 2015, IBM demonstrated 7 nm node chips with silicon–germanium transistors produced using EUVL. The company believed this transistor density would be four times that of the then current 14 nm chips.[83]

- Samsung and TSMC plan to manufacture 3 nm GAAFET nodes by 2021–2022.[84][85] Note that node names, such as 3 nm, have no relation to the physical size of device elements (transistors).

- A Toshiba research team including T. Imoto, M. Matsui and C. Takubo developed a "System Block Module" wafer bonding process for manufacturing three-dimensional integrated circuit (3D IC) packages in 2001.[86][87] In April 2007, Toshiba introduced an eight-layer 3D IC, the 16 GB THGAM embedded NAND flash memory chip that was manufactured with eight stacked 2 GB NAND flash chips.[88] In September 2007, Hynix introduced 24-layer 3D IC, a 16 GB flash memory chip that was manufactured with 24 stacked NAND flash chips using a wafer bonding process.[89]

- V-NAND, also known as 3D NAND, allows flash memory cells to be stacked vertically using charge trap flash technology originally presented by John Szedon in 1967, significantly increasing the number of transistors on a flash memory chip. 3D NAND was first announced by Toshiba in 2007.[90] V-NAND was first commercially manufactured by Samsung Electronics in 2013.[91][92][93]

- In 2008, researchers at HP Labs announced a working memristor, a fourth basic passive circuit element whose existence only had been theorized previously. The memristor's unique properties permit the creation of smaller and better-performing electronic devices.[94]

- In 2014, bioengineers at Stanford University developed a circuit modeled on the human brain. Sixteen "Neurocore" chips simulate one million neurons and billions of synaptic connections, claimed to be 9000 times faster as well as more energy efficient than a typical PC.[95]

- In 2015, Intel and Micron announced 3D XPoint, a non-volatile memory claimed to be significantly faster with similar density compared to NAND. Production scheduled to begin in 2016 was delayed until the second half of 2017.[96][97][98]

- In 2017, Samsung combined its V-NAND technology with eUFS 3D IC stacking to produce a 512 GB flash memory chip, with eight stacked 64-layer V-NAND dies.[99] In 2019, Samsung produced a 1 TB flash chip with eight stacked 96-layer V-NAND dies, along with quad-level cell (QLC) technology (4-bit per transistor),[100][101] equivalent to 2 trillion transistors, the highest transistor count of any IC chip.

- In 2020, Samsung Electronics planned to produce the 5 nm node, using FinFET and EUV technology.[36][needs update]

- In May 2021, IBM announced the creation of the first 2 nm computer chip, with parts supposedly being smaller than human DNA.[102]

Microprocessor architects report that semiconductor advancement has slowed industry-wide since around 2010, below the pace predicted by Moore's law.[17] Brian Krzanich, the former CEO of Intel, announced, "Our cadence today is closer to two and a half years than two."[103] Intel stated in 2015 that improvements in MOSFET devices have slowed, starting at the 22 nm feature width around 2012, and continuing at 14 nm.[104] Pat Gelsinger, Intel CEO, stated at the end of 2023 that "we're no longer in the golden era of Moore's Law, it's much, much harder now, so we're probably doubling effectively closer to every three years now, so we've definitely seen a slowing."[105]

The physical limits to transistor scaling have been reached due to source-to-drain leakage, limited gate metals and limited options for channel material. Other approaches are being investigated, which do not rely on physical scaling. These include the spin state of electron spintronics, tunnel junctions, and advanced confinement of channel materials via nano-wire geometry.[106] Spin-based logic and memory options are being developed actively in labs.[107][108]

Alternative materials research

[edit]The vast majority of current transistors on ICs are composed principally of doped silicon and its alloys. As silicon is fabricated into single nanometer transistors, short-channel effects adversely change desired material properties of silicon as a functional transistor. Below are several non-silicon substitutes in the fabrication of small nanometer transistors.

One proposed material is indium gallium arsenide, or InGaAs. Compared to their silicon and germanium counterparts, InGaAs transistors are more promising for future high-speed, low-power logic applications. Because of intrinsic characteristics of III–V compound semiconductors, quantum well and tunnel effect transistors based on InGaAs have been proposed as alternatives to more traditional MOSFET designs.

- In the early 2000s, the atomic layer deposition high-κ film and pitch double-patterning processes were invented by Gurtej Singh Sandhu at Micron Technology, extending Moore's law for planar CMOS technology to 30 nm class and smaller.

- In 2009, Intel announced the development of 80 nm InGaAs quantum well transistors. Quantum well devices contain a material sandwiched between two layers of material with a wider band gap. Despite being double the size of leading pure silicon transistors at the time, the company reported that they performed equally as well while consuming less power.[109]

- In 2011, researchers at Intel demonstrated 3-D tri-gate InGaAs transistors with improved leakage characteristics compared to traditional planar designs. The company claims that their design achieved the best electrostatics of any III–V compound semiconductor transistor.[110] At the 2015 International Solid-State Circuits Conference, Intel mentioned the use of III–V compounds based on such an architecture for their 7 nm node.[111][112]

- In 2011, researchers at the University of Texas at Austin developed an InGaAs tunneling field-effect transistors capable of higher operating currents than previous designs. The first III–V TFET designs were demonstrated in 2009 by a joint team from Cornell University and Pennsylvania State University.[113][114]

- In 2012, a team in MIT's Microsystems Technology Laboratories developed a 22 nm transistor based on InGaAs that, at the time, was the smallest non-silicon transistor ever built. The team used techniques used in silicon device fabrication and aimed for better electrical performance and a reduction to 10-nanometer scale.[115]

Biological computing research shows that biological material has superior information density and energy efficiency compared to silicon-based computing.[116]

Various forms of graphene are being studied for graphene electronics, e.g. graphene nanoribbon transistors have shown promise since its appearance in publications in 2008. (Bulk graphene has a band gap of zero and thus cannot be used in transistors because of its constant conductivity, an inability to turn off. The zigzag edges of the nanoribbons introduce localized energy states in the conduction and valence bands and thus a bandgap that enables switching when fabricated as a transistor. As an example, a typical GNR of width of 10 nm has a desirable bandgap energy of 0.4 eV.[117][118]) More research will need to be performed, however, on sub-50 nm graphene layers, as its resistivity value increases and thus electron mobility decreases.[117]

Forecasts and roadmaps

[edit]In April 2005, Gordon Moore stated in an interview that the projection cannot be sustained indefinitely: "It can't continue forever. The nature of exponentials is that you push them out and eventually disaster happens." He also noted that transistors eventually would reach the limits of miniaturization at atomic levels:

In terms of size [of transistors] you can see that we're approaching the size of atoms which is a fundamental barrier, but it'll be two or three generations before we get that far—but that's as far out as we've ever been able to see. We have another 10 to 20 years before we reach a fundamental limit. By then they'll be able to make bigger chips and have transistor budgets in the billions.[119]

— Gordon Moore in 2006

In 2016 the International Technology Roadmap for Semiconductors, after using Moore's Law to drive the industry since 1998, produced its final roadmap. It no longer centered its research and development plan on Moore's law. Instead, it outlined what might be called the More than Moore strategy in which the needs of applications drive chip development, rather than a focus on semiconductor scaling. Application drivers range from smartphones to AI to data centers.[120]

IEEE began a road-mapping initiative in 2016, "Rebooting Computing", named the International Roadmap for Devices and Systems (IRDS).[121]

Some forecasters, including Gordon Moore,[122] predict that Moore's law will end by around 2025.[123][120][124] Although Moore's Law will reach a physical limit, some forecasters are optimistic about the continuation of technological progress in a variety of other areas, including new chip architectures, quantum computing, and AI and machine learning.[125][126] Nvidia CEO Jensen Huang declared Moore's law dead in 2022;[2] several days later, Intel CEO Pat Gelsinger countered with the opposite claim.[3]

Consequences

[edit]Digital electronics have contributed to world economic growth in the late twentieth and early twenty-first centuries.[127] The primary driving force of economic growth is the growth of productivity,[128] which Moore's law factors into. Moore (1995) expected that "the rate of technological progress is going to be controlled from financial realities".[129] The reverse could and did occur around the late-1990s, however, with economists reporting that "Productivity growth is the key economic indicator of innovation."[130] Moore's law describes a driving force of technological and social change, productivity, and economic growth.[131][132][128]

An acceleration in the rate of semiconductor progress contributed to a surge in U.S. productivity growth,[133][134][135] which reached 3.4% per year in 1997–2004, outpacing the 1.6% per year during both 1972–1996 and 2005–2013.[136] As economist Richard G. Anderson notes, "Numerous studies have traced the cause of the productivity acceleration to technological innovations in the production of semiconductors that sharply reduced the prices of such components and of the products that contain them (as well as expanding the capabilities of such products)."[137]

The primary negative implication of Moore's law is that obsolescence pushes society up against the Limits to Growth. As technologies continue to rapidly "improve", they render predecessor technologies obsolete. In situations in which security and survivability of hardware or data are paramount, or in which resources are limited, rapid obsolescence often poses obstacles to smooth or continued operations.[138]

Other formulations and similar observations

[edit]Several measures of digital technology are improving at exponential rates related to Moore's law, including the size, cost, density, and speed of components. Moore wrote only about the density of components, "a component being a transistor, resistor, diode or capacitor",[129] at minimum cost.

Transistors per integrated circuit – The most popular formulation is of the doubling of the number of transistors on ICs every two years. At the end of the 1970s, Moore's law became known as the limit for the number of transistors on the most complex chips. The graph at the top of this article shows this trend holds true today. As of 2017[update], the commercially available processor possessing the highest number of transistors is the 48 core Centriq with over 18 billion transistors.[139]

Density at minimum cost per transistor – This is the formulation given in Moore's 1965 paper.[1] It is not just about the density of transistors that can be achieved, but about the density of transistors at which the cost per transistor is the lowest.[140]

As more transistors are put on a chip, the cost to make each transistor decreases, but the chance that the chip will not work due to a defect increases. In 1965, Moore examined the density of transistors at which cost is minimized, and observed that, as transistors were made smaller through advances in photolithography, this number would increase at "a rate of roughly a factor of two per year".[1]

Dennard scaling – This posits that power usage would decrease in proportion to area (both voltage and current being proportional to length) of transistors. Combined with Moore's law, performance per watt would grow at roughly the same rate as transistor density, doubling every 1–2 years. According to Dennard scaling transistor dimensions would be scaled by 30% (0.7×) every technology generation, thus reducing their area by 50%. This would reduce the delay by 30% (0.7×) and therefore increase operating frequency by about 40% (1.4×). Finally, to keep electric field constant, voltage would be reduced by 30%, reducing energy by 65% and power (at 1.4× frequency) by 50%.[c] Therefore, in every technology generation transistor density would double, circuit becomes 40% faster, while power consumption (with twice the number of transistors) stays the same.[141] Dennard scaling ended in 2005–2010, due to leakage currents.[17]

The exponential processor transistor growth predicted by Moore does not always translate into exponentially greater practical CPU performance. Since around 2005–2007, Dennard scaling has ended, so even though Moore's law continued after that, it has not yielded proportional dividends in improved performance.[15][142] The primary reason cited for the breakdown is that at small sizes, current leakage poses greater challenges, and also causes the chip to heat up, which creates a threat of thermal runaway and therefore, further increases energy costs.[15][142][17]

The breakdown of Dennard scaling prompted a greater focus on multicore processors, but the gains offered by switching to more cores are lower than the gains that would be achieved had Dennard scaling continued.[143][144] In another departure from Dennard scaling, Intel microprocessors adopted a non-planar tri-gate FinFET at 22 nm in 2012 that is faster and consumes less power than a conventional planar transistor.[145] The rate of performance improvement for single-core microprocessors has slowed significantly.[146] Single-core performance was improving by 52% per year in 1986–2003 and 23% per year in 2003–2011, but slowed to just seven percent per year in 2011–2018.[146]

Quality adjusted price of IT equipment – The price of information technology (IT), computers and peripheral equipment, adjusted for quality and inflation, declined 16% per year on average over the five decades from 1959 to 2009.[147][148] The pace accelerated, however, to 23% per year in 1995–1999 triggered by faster IT innovation,[130] and later, slowed to 2% per year in 2010–2013.[147][149]

While quality-adjusted microprocessor price improvement continues,[150] the rate of improvement likewise varies, and is not linear on a log scale. Microprocessor price improvement accelerated during the late 1990s, reaching 60% per year (halving every nine months) versus the typical 30% improvement rate (halving every two years) during the years earlier and later.[151][152] Laptop microprocessors in particular improved 25–35% per year in 2004–2010, and slowed to 15–25% per year in 2010–2013.[153]

The number of transistors per chip cannot explain quality-adjusted microprocessor prices fully.[151][154][155] Moore's 1995 paper does not limit Moore's law to strict linearity or to transistor count, "The definition of 'Moore's Law' has come to refer to almost anything related to the semiconductor industry that on a semi-log plot approximates a straight line. I hesitate to review its origins and by doing so restrict its definition."[129]

Hard disk drive areal density – A similar prediction (sometimes called Kryder's law) was made in 2005 for hard disk drive areal density.[156] The prediction was later viewed as over-optimistic. Several decades of rapid progress in areal density slowed around 2010, from 30 to 100% per year to 10–15% per year, because of noise related to smaller grain size of the disk media, thermal stability, and writability using available magnetic fields.[157][158]

Fiber-optic capacity – The number of bits per second that can be sent down an optical fiber increases exponentially, faster than Moore's law. Keck's law, in honor of Donald Keck.[159]

Network capacity – According to Gerald Butters,[160][161] the former head of Lucent's Optical Networking Group at Bell Labs, there is another version, called Butters' Law of Photonics,[162] a formulation that deliberately parallels Moore's law. Butters' law says that the amount of data coming out of an optical fiber is doubling every nine months.[163] Thus, the cost of transmitting a bit over an optical network decreases by half every nine months. The availability of wavelength-division multiplexing (sometimes called WDM) increased the capacity that could be placed on a single fiber by as much as a factor of 100. Optical networking and dense wavelength-division multiplexing (DWDM) is rapidly bringing down the cost of networking, and further progress seems assured. As a result, the wholesale price of data traffic collapsed in the dot-com bubble. Nielsen's Law says that the bandwidth available to users increases by 50% annually.[164]

Pixels per dollar – Similarly, Barry Hendy of Kodak Australia has plotted pixels per dollar as a basic measure of value for a digital camera, demonstrating the historical linearity (on a log scale) of this market and the opportunity to predict the future trend of digital camera price, LCD and LED screens, and resolution.[165][166][167][168]

The great Moore's law compensator (TGMLC), also known as Wirth's law – generally is referred to as software bloat and is the principle that successive generations of computer software increase in size and complexity, thereby offsetting the performance gains predicted by Moore's law. In a 2008 article in InfoWorld, Randall C. Kennedy,[169] formerly of Intel, introduces this term using successive versions of Microsoft Office between the year 2000 and 2007 as his premise. Despite the gains in computational performance during this time period according to Moore's law, Office 2007 performed the same task at half the speed on a prototypical year 2007 computer as compared to Office 2000 on a year 2000 computer.

Library expansion – was calculated in 1945 by Fremont Rider to double in capacity every 16 years, if sufficient space were made available.[170] He advocated replacing bulky, decaying printed works with miniaturized microform analog photographs, which could be duplicated on-demand for library patrons or other institutions. He did not foresee the digital technology that would follow decades later to replace analog microform with digital imaging, storage, and transmission media. Automated, potentially lossless digital technologies allowed vast increases in the rapidity of information growth in an era that now sometimes is called the Information Age.

Carlson curve – is a term coined by The Economist[171] to describe the biotechnological equivalent of Moore's law, and is named after author Rob Carlson.[172] Carlson accurately predicted that the doubling time of DNA sequencing technologies (measured by cost and performance) would be at least as fast as Moore's law.[173] Carlson Curves illustrate the rapid (in some cases hyperexponential) decreases in cost, and increases in performance, of a variety of technologies, including DNA sequencing, DNA synthesis, and a range of physical and computational tools used in protein expression and in determining protein structures.

Eroom's law – is a pharmaceutical drug development observation that was deliberately written as Moore's Law spelled backwards in order to contrast it with the exponential advancements of other forms of technology (such as transistors) over time. It states that the cost of developing a new drug roughly doubles every nine years.

Experience curve effects says that each doubling of the cumulative production of virtually any product or service is accompanied by an approximate constant percentage reduction in the unit cost. The acknowledged first documented qualitative description of this dates from 1885.[174][175] A power curve was used to describe this phenomenon in a 1936 discussion of the cost of airplanes.[176]

Edholm's law – Phil Edholm observed that the bandwidth of telecommunication networks (including the Internet) is doubling every 18 months.[177] The bandwidths of online communication networks has risen from bits per second to terabits per second. The rapid rise in online bandwidth is largely due to the same MOSFET scaling that enabled Moore's law, as telecommunications networks are built from MOSFETs.[178]

Haitz's law predicts that the brightness of LEDs increases as their manufacturing cost goes down.

Swanson's law is the observation that the price of solar photovoltaic modules tends to drop 20 percent for every doubling of cumulative shipped volume. At present rates, costs go down 75% about every 10 years.

See also

[edit]- Accelerating change – Perceived increase in the rate of technological change throughout history

- Beyond CMOS – Possible future digital logic technologies

- Ephemeralization – Technological advancement theory

- Eroom's law – Observation about the discovery of new drugs

- Huang's law – Computer science observation

- Koomey's law – Trend indicating the number of computations per unit energy dissipated doubles every 1.57 years

- Limits of computation – Overview of the limits of computation

- List of eponymous laws – Adages and sayings named after a person

- List of laws § Technology

- Microprocessor chronology – Timeline of microprocessors

- Neural scaling law – Law in machine learning

- Power law – Functional relationship between two quantities

- Wirth's law – Computing adage made popular by Niklaus Wirth

- Rent's rule – Relationship between the number of external signal with the number of logic gates in a logic block

Explanatory notes

[edit]- ^ The trend begins with the invention of the integrated circuit in 1958. See the graph on the bottom of page 3 of Moore's original presentation of the idea.[1]

- ^ In April 2005, Intel offered US$10,000 to purchase a copy of the original Electronics issue in which Moore's article appeared.[10] An engineer living in the United Kingdom was the first to find a copy and offer it to Intel.[11]

- ^ Active power = CV2f

References

[edit]- ^ a b c d e Moore, Gordon E. (April 19, 1965). "Cramming more components onto integrated circuits" (PDF). intel.com. Electronics Magazine. Archived (PDF) from the original on March 27, 2019. Retrieved April 1, 2020.

- ^ a b Witkowski, Wallace (September 22, 2022). "'Moore's Law's dead,' Nvidia CEO Jensen Huang says in justifying gaming-card price hike". MarketWatch. Retrieved September 23, 2022.

- ^ a b Machkovech, Sam (September 27, 2022). "Intel: 'Moore's law is not dead' as Arc A770 GPU is priced at $329". Ars Technica. Retrieved September 28, 2022.

- ^ Engelbart, Douglas C. (February 12, 1960). "Microelectronics and the art of similitude". 1960 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. Vol. III. IEEE. pp. 76–77. doi:10.1109/ISSCC.1960.1157297. Archived from the original on June 20, 2018.

- ^ Markoff, John (April 18, 2005). "It's Moore's Law But Another Had The Idea First". The New York Times. Archived from the original on March 4, 2012. Retrieved October 4, 2011.

- ^ Markoff, John (August 31, 2009). "After the Transistor, a Leap into the Microcosm". The New York Times. Retrieved August 31, 2009.

- ^ Markoff, John (September 27, 2015). "Smaller, Faster, Cheaper, Over: The Future of Computer Chips". The New York Times. Retrieved September 28, 2015.

- ^ Kovacich, Gerald L. (2016). The Information Systems Security Officer's Guide: Establishing and Managing a Cyber Security Program (3rd ed.). Oxford: Butterworth-Heinemann. p. 72. ISBN 978-0-12-802190-3.

- ^ "Excerpts from a conversation with Gordon Moore: Moore's Law" (PDF). Intel Corporation. 2005. p. 1. Archived from the original (PDF) on October 29, 2012. Retrieved April 1, 2020.

- ^ Kanellos, Michael (April 11, 2005). "Intel offers $10,000 for Moore's Law magazine". ZDNET News.com. Retrieved June 21, 2013.

- ^ "Moore's Law original issue found". BBC News Online. April 22, 2005. Retrieved August 26, 2012.

- ^ a b Schaller, Bob (September 26, 1996). "The Origin, Nature, and Implications of 'MOORE'S LAW'". Microsoft. Retrieved September 10, 2014.

- ^ a b c Tuomi, I. (2002). "The Lives and Death of Moore's Law". First Monday. 7 (11). doi:10.5210/fm.v7i11.1000.

- ^

Moore, Gordon (March 30, 2015). "Gordon Moore: The Man Whose Name Means Progress, The visionary engineer reflects on 50 years of Moore's Law". IEEE Spectrum: Special Report: 50 Years of Moore's Law (Interview). Interviewed by Rachel Courtland.

We won't have the rate of progress that we've had over the last few decades. I think that's inevitable with any technology; it eventually saturates out. I guess I see Moore's law dying here in the next decade or so, but that's not surprising.

- ^ a b c McMenamin, Adrian (April 15, 2013). "The end of Dennard scaling". Retrieved January 23, 2014.

- ^ Streetman, Ben G.; Banerjee, Sanjay Kumar (2016). Solid state electronic devices. Boston: Pearson. p. 341. ISBN 978-1-292-06055-2. OCLC 908999844.

- ^ a b c d e f g John L. Hennessy; David A. Patterson (June 4, 2018). "A New Golden Age for Computer Architecture: Domain-Specific Hardware/Software Co-Design, Enhanced Security, Open Instruction Sets, and Agile Chip Development". International Symposium on Computer Architecture – ISCA 2018.

In the later 1990s and 2000s, architectural innovation decreased, so performance came primarily from higher clock rates and larger caches. The ending of Dennard Scaling and Moore's Law also slowed this path; single core performance improved only 3% last year!

- ^ Takahashi, Dean (April 18, 2005). "Forty years of Moore's law". Seattle Times. San Jose, California. Retrieved April 7, 2015.

A decade later, he revised what had become known as Moore's Law: The number of transistors on a chip would double every two years.

- ^ a b Moore, Gordon (1975). "IEEE Technical Digest 1975" (PDF). Intel Corp. Archived (PDF) from the original on October 9, 2022. Retrieved April 7, 2015.

... the rate of increase of complexity can be expected to change slope in the next few years as shown in Figure 5. The new slope might approximate a doubling every two years, rather than every year, by the end of the decade.

- ^ Moore, Gordon (2006). "Chapter 7: Moore's law at 40" (PDF). In Brock, David (ed.). Understanding Moore's Law: Four Decades of Innovation. Chemical Heritage Foundation. pp. 67–84. ISBN 978-0-941901-41-3. Archived from the original (PDF) on March 4, 2016. Retrieved March 22, 2018.

- ^ "Over 6 Decades of Continued Transistor Shrinkage, Innovation" (PDF) (Press release). Intel Corporation. May 2011. Archived from the original on June 17, 2012. Retrieved March 25, 2023.

1965: Moore's Law is born when Gordon Moore predicts that the number of transistors on a chip will double roughly every year (a decade later, in 1975, Moore published an update, revising the doubling period to every 2 years)

- ^ Brock, David C., ed. (2006). Understanding Moore's law: four decades of innovation. Philadelphia, Pennsylvania: Chemical Heritage Foundation. ISBN 978-0941901413.

- ^ "Moore's Law at 40 – Happy birthday". The Economist. March 23, 2005. Retrieved June 24, 2006.

- ^ a b Disco, Cornelius; van der Meulen, Barend (1998). Getting new technologies together. Walter de Gruyter. pp. 206–7. ISBN 978-3-11-015630-0. OCLC 39391108. Retrieved August 23, 2008.

- ^ "Gordon Moore Says Aloha to Moore's Law". the Inquirer. April 13, 2005. Archived from the original on November 6, 2009. Retrieved September 2, 2009.

- ^ Meador, Dan; Goldsmith, Kevin (2022). Building Data Science Solutions with Anaconda: A comprehensive starter guide to building robust and complete models. Birmingham, UK: Packt Publishing Limited. p. 9. ISBN 978-1-80056-878-5.

- ^ "The Immutable Connection between Moore's Law and Artificial Intelligence". Technowize Magazine. May 2017. Retrieved August 24, 2018.

- ^ "Moore's Law to roll on for another decade". Retrieved November 27, 2011.

Moore also affirmed he never said transistor count would double every 18 months, as is commonly said. Initially, he said transistors on a chip would double every year. He then recalibrated it to every two years in 1975. David House, an Intel executive at the time, noted that the changes would cause computer performance to double every 18 months.

- ^ Sandhie, Zarin Tasnim; Ahmed, Farid Uddin; Chowdhury, Masud H. (2022). Beyond Binary Memory Circuits: Multiple-Valued Logic. Cham, Switzerland: Springer Nature. p. 1. ISBN 978-3-031-16194-0.

- ^ Bradshaw, Tim (July 16, 2015). "Intel chief raises doubts over Moore's law". Financial Times. Retrieved July 16, 2015.

- ^ Waters, Richard (July 16, 2015). "As Intel co-founder's law slows, a rethinking of the chip is needed". Financial Times.

- ^ Niccolai, James (July 15, 2015). "Intel pushes 10nm chip-making process to 2017, slowing Moore's Law". Infoworld. Retrieved July 16, 2015.

It's official: Moore's Law is slowing down. ... "These transitions are a natural part of the history of Moore's Law and are a by-product of the technical challenges of shrinking transistors while ensuring they can be manufactured in high volume", Krzanich said.

- ^ Conte, Thomas M.; Track, Elie; DeBenedictis, Erik (December 2015). "Rebooting Computing: New Strategies for Technology Scaling". Computer. 48 (12): 10–13. doi:10.1109/MC.2015.363. S2CID 43750026.

Year-over-year exponential computer performance scaling has ended. Complicating this is the coming disruption of the "technology escalator" underlying the industry: Moore's law.

- ^ a b Shilov, Anton (October 23, 2019). "TSMC: 5nm on Track for Q2 2020 HVM, Will Ramp Faster Than 7nm". www.anandtech.com. Retrieved December 1, 2019.

- ^ a b c Shilov, Anton (July 31, 2019). "Home>Semiconductors Samsung's Aggressive EUV Plans: 6nm Production in H2, 5nm & 4nm On Track". www.anandtech.com. Retrieved December 1, 2019.

- ^ Cheng, Godfrey (August 14, 2019). "Moore's Law is not Dead". TSMC Blog. TSMC. Retrieved August 18, 2019.

- ^ Martin, Eric (June 4, 2019). "Moore's Law is Alive and Well – Charts show it may be dying at Intel, but others are picking up the slack". Medium. Archived from the original on August 25, 2019. Retrieved July 19, 2019.

- ^ "5nm Vs. 3nm". Semiconductor Engineering. June 24, 2019. Retrieved July 19, 2019.

- ^ Lilly, Paul (July 17, 2019). "Intel says it was too aggressive pursuing 10nm, will have 7nm chips in 2021". PC Gamer.

- ^ Shilov, Anton. "Samsung Completes Development of 5nm EUV Process Technology". anandtech.com. Retrieved May 31, 2019.

- ^ TSMC and OIP Ecosystem Partners Deliver Industry's First Complete Design Infrastructure for 5nm Process Technology (press release), TSMC, April 3, 2019, archived from the original on May 14, 2020, retrieved July 19, 2019

- ^ Cutress, Dr. Ian. "'Better Yield on 5nm than 7nm': TSMC Update on Defect Rates for N5". www.anandtech.com. Retrieved March 27, 2023.

- ^ VerWey, John (July 2019). The Health and Competitiveness of the U.S. Semiconductor Manufacturing Equipment Industry (PDF) (Report). U.S. International Trade Commission. p. 17. Retrieved April 30, 2024.

The costs required to fabricate chips have increased in a predictable manner, operating under what is referred to Moore's Second Law or "Rock's Law", which says the cost of semiconductor tools doubles every four years.

- ^ Lemon, Sumner; Krazit, Tom (April 19, 2005). "With chips, Moore's Law is not the problem". Infoworld. Retrieved August 22, 2011.

- ^ Dorsch, Jeff. "Does Moore's Law Still Hold Up?" (PDF). EDA Vision. Archived from the original (PDF) on May 6, 2006. Retrieved August 22, 2011.

- ^ Schaller, Bob (September 26, 1996). "The Origin, Nature, and Implications of 'Moore's Law'". Research.microsoft.com. Retrieved August 22, 2011.

- ^ Kilby, Jack, "Miniaturized electronic circuits", US 3138743, issued June 23, 1964 (filed February 6, 1959).

- ^ Noyce, Robert, "Semiconductor device-and-lead structure", US 2981877, issued April 25, 1961 (filed July 30, 1959).

- ^ "1963: Complementary MOS Circuit Configuration is Invented". Computer History Museum. Retrieved July 6, 2019.

- ^ Sah, Chih-Tang; Wanlass, Frank (1963). Nanowatt logic using field-effect metal-oxide semiconductor triodes. 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. Vol. VI. pp. 32–33. doi:10.1109/ISSCC.1963.1157450.

- ^ Wanlass, F., "Low stand-by power complementary field effect circuitry", US 3356858, issued December 5, 1967 (filed June 18, 1963).

- ^ Dennard, Robert H., "Field-effect transistor memory", US 3387286, issued June 4, 1968 (filed July 14, 1967)

- ^ U.S. patent 4,491,628, "Positive and Negative Working Resist Compositions with Acid-Generating Photoinitiator and Polymer with Acid-Labile Groups Pendant From Polymer Backbone" J. M. J. Fréchet, H. Ito and C. G. Willson 1985.[1], Archived February 2, 2019, at the Wayback Machine.

- ^ Ito, H.; Willson, C. G. (1983). "Chemical amplification in the design of dry developing resist material". Polymer Engineering & Science. 23 (18): 204. doi:10.1002/pen.760231807.

- ^ Ito, Hiroshi; Willson, C. Grant; Frechet, Jean H. J. (1982). "New UV resists with negative or positive tone". VLSI Technology, 1982. Digest of Technical Papers. Symposium on.

- ^ Brock, David C. (October 1, 2007). "Patterning the World: The Rise of Chemically Amplified Photoresists". Chemical Heritage Magazine. Chemical Heritage Foundation. Retrieved March 27, 2018.

- ^ Lamola, A. A.; Szmanda, C. R.; Thackeray, J. W. (August 1991). "Chemically amplified resists". Solid State Technology. 34 (8). Retrieved November 1, 2017.

- ^ Ito, Hiroshi (2000). "Chemical amplification resists: History and development within IBM" (PDF). IBM Journal of Research and Development. Archived (PDF) from the original on October 9, 2022. Retrieved May 20, 2014.

- ^ 4458994 A US patent US 4458994 A, Kantilal Jain, Carlton G. Willson, "High resolution optical lithography method and apparatus having excimer laser light source and stimulated Raman shifting", issued 1984-07-10.

- ^ Jain, K.; Willson, C. G.; Lin, B. J. (1982). "Ultrafast deep-UV lithography with excimer lasers". IEEE Electron Device Letters. 3 (3): 53–55. Bibcode:1982IEDL....3...53J. doi:10.1109/EDL.1982.25476. S2CID 43335574.

- ^ Jain, K. (1990). Excimer Laser Lithography. Bellingham, Washington: SPIE Press. ISBN 978-0-8194-0271-4. OCLC 20492182.

- ^ La Fontaine, Bruno (October 2010). "Lasers and Moore's Law". SPIE Professional. p. 20.

- ^ Basov, N. G. et al., Zh. Eksp. Fiz. i Tekh. Pis'ma. Red. 12, 473 (1970).

- ^ Burnham, R.; Djeu, N. (1976). "Ultraviolet-preionized discharge-pumped lasers in XeF, KrF, and ArF". Appl. Phys. Lett. 29 (11): 707. Bibcode:1976ApPhL..29..707B. doi:10.1063/1.88934.

- ^ Lasers in Our Lives / 50 Years of Impact (PDF), U.K. Engineering and Physical Sciences Research Council, archived from the original (PDF) on September 13, 2011, retrieved August 22, 2011

- ^ "50 Years Advancing the Laser" (PDF). SPIE. Archived (PDF) from the original on October 9, 2022. Retrieved August 22, 2011.

- ^ Moore, Gordon E. (February 10, 2003). "transcription of Gordon Moore's Plenary Address at ISSCC 50th Anniversary" (PDF). transcription "Moore on Moore: no Exponential is forever". 2003 IEEE International Solid-State Circuits Conference. San Francisco, California: ISSCC. Archived from the original (PDF) on March 31, 2010.

- ^ Steigerwald, J. M. (2008). "Chemical mechanical polish: The enabling technology". 2008 IEEE International Electron Devices Meeting. pp. 1–4. doi:10.1109/IEDM.2008.4796607. ISBN 978-1-4244-2377-4. S2CID 8266949. "Table1: 1990 enabling multilevel metallization; 1995 enabling STI compact isolation, polysilicon patterning and yield / defect reduction"

- ^ "IBM100 – Copper Interconnects: The Evolution of Microprocessors". March 7, 2012. Archived from the original on April 3, 2012. Retrieved October 17, 2012.

- ^ "International Technology Roadmap for Semiconductors". Archived from the original on August 25, 2011. Retrieved August 22, 2011.

- ^ Masuoka, Fujio; Takato, H.; Sunouchi, K.; Okabe, N.; Nitayama, A.; Hieda, K.; Horiguchi, F. (December 1988). "High performance CMOS surrounding gate transistor (SGT) for ultra high density LSIs". Technical Digest., International Electron Devices Meeting. pp. 222–225. doi:10.1109/IEDM.1988.32796. S2CID 114148274.

- ^ Brozek, Tomasz (2017). Micro- and Nanoelectronics: Emerging Device Challenges and Solutions. CRC Press. p. 117. ISBN 9781351831345.

- ^ "Company Profile". Unisantis Electronics. Archived from the original on February 22, 2007. Retrieved July 17, 2019.

- ^ "Still Room at the Bottom.(nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology )", Nanoparticle News, April 1, 2006, archived from the original on November 6, 2012

- ^ Lee, Hyunjin; et al. (2006). "Sub-5nm All-Around Gate FinFET for Ultimate Scaling". 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers. pp. 58–59. doi:10.1109/VLSIT.2006.1705215. hdl:10203/698. ISBN 978-1-4244-0005-8. S2CID 26482358.

- ^ Johnson, Dexter (February 22, 2010). "Junctionless Transistor Fabricated from Nanowires". IEEE Spectrum. Retrieved April 20, 2010.

- ^ Cheng, Guanglei; Siles, Pablo F.; Bi, Feng; Cen, Cheng; Bogorin, Daniela F.; Bark, Chung Wung; Folkman, Chad M.; Park, Jae-Wan; Eom, Chang-Beom; Medeiros-Ribeiro, Gilberto; Levy, Jeremy (April 19, 2011). "Super-small transistor created: Artificial atom powered by single electron". Nature Nanotechnology. 6 (6): 343–347. Bibcode:2011NatNa...6..343C. doi:10.1038/nnano.2011.56. PMID 21499252. Retrieved August 22, 2011.

- ^ Kaku, Michio (2010). Physics of the Future. Doubleday. p. 173. ISBN 978-0-385-53080-4.

- ^ Yirka, Bob (May 2, 2013). "New nanowire transistors may help keep Moore's Law alive". Nanoscale. 5 (6): 2437–2441. Bibcode:2013Nanos...5.2437L. doi:10.1039/C3NR33738C. PMID 23403487. Retrieved August 8, 2013.

- ^ "Rejuvenating Moore's Law With Nanotechnology". Forbes. June 5, 2007. Retrieved August 8, 2013.

- ^ Fuechsle, M.; Miwa, J. A.; Mahapatra, S.; Ryu, H.; Lee, S.; Warschkow, O.; Hollenberg, L. C.; Klimeck, G.; Simmons, M. Y. (December 16, 2011). "A single-atom transistor". Nat Nanotechnol. 7 (4): 242–246. Bibcode:2012NatNa...7..242F. doi:10.1038/nnano.2012.21. PMID 22343383. S2CID 14952278.

- ^ "IBM Reports Advance in Shrinking Chip Circuitry". The Wall Street Journal. July 9, 2015. Retrieved July 9, 2015.

- ^ Armasu, Lucian (January 11, 2019), "Samsung Plans Mass Production of 3nm GAAFET Chips in 2021", www.tomshardware.com

- ^ Patterson, Alan (October 2, 2017), "TSMC Aims to Build World's First 3-nm Fab", www.eetimes.com

- ^ Garrou, Philip (August 6, 2008). "Introduction to 3D Integration" (PDF). Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits. Wiley-VCH. p. 4. doi:10.1002/9783527623051.ch1. ISBN 9783527623051. Archived (PDF) from the original on October 9, 2022.

- ^ Imoto, T.; Matsui, M.; Takubo, C.; Akejima, S.; Kariya, T.; Nishikawa, T.; Enomoto, R. (2001). "Development of 3-Dimensional Module Package, "System Block Module"". Electronic Components and Technology Conference (51). Institute of Electrical and Electronics Engineers: 552–557.

- ^ "TOSHIBA COMMERCIALIZES INDUSTRY'S HIGHEST CAPACITY EMBEDDED NAND FLASH MEMORY FOR MOBILE CONSUMER PRODUCTS". Toshiba. April 17, 2007. Archived from the original on November 23, 2010. Retrieved November 23, 2010.

- ^ "Hynix Surprises NAND Chip Industry". Korea Times. September 5, 2007. Retrieved July 8, 2019.

- ^ "Toshiba announces new "3D" NAND flash technology". Engadget. June 12, 2007. Retrieved July 10, 2019.

- ^ "Samsung Introduces World's First 3D V-NAND Based SSD for Enterprise Applications | Samsung | Samsung Semiconductor Global Website". www.samsung.com.

- ^ Clarke, Peter. "Samsung Confirms 24 Layers in 3D NAND". EETimes.

- ^ "Samsung Electronics Starts Mass Production of Industry First 3-bit 3D V-NAND Flash Memory". news.samsung.com.

- ^ Strukov, Dmitri B; Snider, Gregory S; Stewart, Duncan R; Williams, Stanley R (2008). "The missing memristor found". Nature. 453 (7191): 80–83. Bibcode:2008Natur.453...80S. doi:10.1038/nature06932. PMID 18451858. S2CID 4367148.

- ^ "Stanford bioengineers create circuit board modeled on the human brain – Stanford News Release". news.stanford.edu. April 28, 2014. Archived from the original on January 22, 2019. Retrieved May 4, 2014.

- ^ Kelion, Leo (July 28, 2015). "3D Xpoint memory: Faster-than-flash storage unveiled". BBC News.

- ^ "Intel's New Memory Chips Are Faster, Store Way More Data". WIRED. July 28, 2015.

- ^ Bright, Peter (March 19, 2017). "Intel's first Optane SSD: 375GB that you can also use as RAM". Ars Technica. Retrieved March 31, 2017.

- ^ Shilov, Anton (December 5, 2017). "Samsung Starts Production of 512 GB UFS NAND Flash Memory: 64-Layer V-NAND, 860 MB/s Reads". AnandTech. Retrieved June 23, 2019.

- ^ Manners, David (January 30, 2019). "Samsung makes 1TB flash eUFS module". Electronics Weekly. Retrieved June 23, 2019.

- ^ Tallis, Billy (October 17, 2018). "Samsung Shares SSD Roadmap for QLC NAND And 96-layer 3D NAND". AnandTech. Retrieved June 27, 2019.

- ^ IBM (May 6, 2021). "IBM Unveils World's First 2 Nanometer Chip Technology, Opening a New Frontier for Semiconductors". Archived from the original on May 6, 2021. Retrieved May 14, 2021.

- ^ Clark, Don (July 15, 2015). "Intel Rechisels the Tablet on Moore's Law". Wall Street Journal Digits Tech News and Analysis. Retrieved July 16, 2015.

The last two technology transitions have signaled that our cadence today is closer to two and a half years than two

- ^ "INTEL CORP, FORM 10-K (Annual Report), Filed 02/12/16 for the Period Ending 12/26/15" (PDF). Archived from the original (PDF) on December 4, 2018. Retrieved February 24, 2017.

- ^ Connatser, Matthew (December 24, 2023). "Intel's CEO says Moore's Law is slowing to a three-year cadence, but it's not dead yet". Tom's Hardware. Future US. Retrieved April 30, 2024.

...the CEO stated transistors now double closer to every three years, which is actually significantly behind the pace of Moore's Law, which dictated a two-year cadence.

- ^ Nikonov, Dmitri E.; Young, Ian A. (February 1, 2013). Overview of Beyond-CMOS Devices and A Uniform Methodology for Their Benchmarking. Cornell University Library. arXiv:1302.0244. Bibcode:2013arXiv1302.0244N.

- ^ Manipatruni, Sasikanth; Nikonov, Dmitri E.; Young, Ian A. (2016). "Material Targets for Scaling All Spin Logic". Physical Review Applied. 5 (1): 014002. arXiv:1212.3362. Bibcode:2016PhRvP...5a4002M. doi:10.1103/PhysRevApplied.5.014002. S2CID 1541400.

- ^ Behin-Aein, Behtash; Datta, Deepanjan; Salahuddin, Sayeef; Datta, Supriyo (February 28, 2010). "Proposal for an all-spin logic device with built-in memory". Nature Nanotechnology. 5 (4): 266–270. Bibcode:2010NatNa...5..266B. doi:10.1038/nnano.2010.31. PMID 20190748.

- ^ Dewey, G.; Kotlyar, R.; Pillarisetty, R.; Radosavljevic, M.; Rakshit, T.; Then, H.; Chau, R. (December 7, 2009). "Logic performance evaluation and transport physics of Schottky-gate III–V compound semiconductor quantum well field effect transistors for power supply voltages (VCC) ranging from 0.5v to 1.0v". 2009 IEEE International Electron Devices Meeting (IEDM). IEEE. pp. 1–4. doi:10.1109/IEDM.2009.5424314. ISBN 978-1-4244-5639-0. S2CID 41734511.

- ^ Radosavljevic R, et al. (December 5, 2011). "Electrostatics improvement in 3-D tri-gate over ultra-thin body planar InGaAs quantum well field effect transistors with high-K gate dielectric and scaled gate-to-drain/Gate-to-source separation". 2011 International Electron Devices Meeting. IEEE. pp. 33.1.1–33.1.4. doi:10.1109/IEDM.2011.6131661. ISBN 978-1-4577-0505-2. S2CID 37889140.

- ^ Cutress, Ian (February 22, 2015). "Intel at ISSCC 2015: Reaping the Benefits of 14nm and Going Beyond 10nm". Anandtech. Retrieved August 15, 2016.

- ^ Anthony, Sebastian (February 23, 2015). "Intel forges ahead to 10nm, will move away from silicon at 7nm". Ars Technica. Retrieved August 15, 2016.

- ^ Cooke, Mike (April–May 2011). "InGaAs tunnel FET with ON current increased by 61%" (PDF). Vol. 6, no. 6. Semiconductor Today. Retrieved August 15, 2016.

- ^ Zhao, Han; et al. (February 28, 2011). "Improving the on-current of In0.7Ga0.3As tunneling field-effect-transistors by p++/n+ tunneling junction". Applied Physics Letters. 98 (9): 093501. Bibcode:2011ApPhL..98i3501Z. doi:10.1063/1.3559607.

- ^ Knight, Helen (October 12, 2012). "Tiny compound semiconductor transistor could challenge silicon's dominance". MIT News. Retrieved August 15, 2016.

- ^ Cavin, R. K.; Lugli, P.; Zhirnov, V. V. (May 1, 2012). "Science and Engineering Beyond Moore's Law". Proceedings of the IEEE. 100 (Special Centennial Issue): 1720–1749. doi:10.1109/JPROC.2012.2190155.

- ^ a b Avouris, Phaedon; Chen, Zhihong; Perebeinos, Vasili (September 30, 2007). "Carbon-based electronics" (PDF). Nature Nanotechnology. 2 (10): 605–615. Bibcode:2007NatNa...2..605A. doi:10.1038/nnano.2007.300. PMID 18654384. Retrieved August 15, 2016.

- ^ Schwierz, Frank (November 1–4, 2011). Graphene Transistors – A New Contender for Future Electronics. 10th IEEE International Conference 2010: Solid-State and Integrated Circuit Technology (ICSICT). Shanghai. doi:10.1109/ICSICT.2010.5667602.

- ^ Dubash, Manek (April 13, 2005). "Moore's Law is dead, says Gordon Moore". Techworld. Retrieved June 24, 2006.

- ^ a b Waldrop, M. Mitchell (February 9, 2016). "The chips are down for Moore's law". Nature. 530 (7589): 144–147. Bibcode:2016Natur.530..144W. doi:10.1038/530144a. ISSN 0028-0836. PMID 26863965.

- ^ "IRDS launch announcement 4 MAY 2016" (PDF). Archived (PDF) from the original on May 27, 2016.

- ^ Cross, Tim. "After Moore's Law". The Economist Technology Quarterly. Retrieved March 13, 2016.

chart: "Faith no Moore" Selected predictions for the end of Moore's law

- ^ Kumar, Suhas (2012). "Fundamental Limits to Moore's Law". arXiv:1511.05956 [cond-mat.mes-hall].

- ^ "Smaller, Faster, Cheaper, Over: The Future of Computer Chips". New York Times. September 2015.

- ^ "The End of More – the Death of Moore's Law". March 6, 2020.

- ^ "These 3 Computing Technologies Will Beat Moore's Law". Forbes.

- ^ Rauch, Jonathan (January 2001). "The New Old Economy: Oil, Computers, and the Reinvention of the Earth". The Atlantic Monthly. Retrieved November 28, 2008.

- ^ a b Kendrick, John W. (1961). Productivity Trends in the United States. Princeton University Press for NBER. p. 3.

- ^ a b c Moore, Gordon E. (1995). "Lithography and the future of Moore's law" (PDF). SPIE. Archived (PDF) from the original on October 9, 2022. Retrieved May 27, 2014.

- ^ a b Jorgenson, Dale W.; Ho, Mun S.; Samuels, Jon D. (2014). "Long-term Estimates of U.S. Productivity and Growth" (PDF). World KLEMS Conference. Archived (PDF) from the original on October 9, 2022. Retrieved May 27, 2014.

- ^ Keyes, Robert W. (September 2006). "The Impact of Moore's Law". Solid State Circuits Newsletter. Vol. 11, no. 3. pp. 25–27. doi:10.1109/N-SSC.2006.4785857.

- ^ Liddle, David E. (September 2006). "The Wider Impact of Moore's Law". Solid State Circuits Newsletter. 11 (3): 28–30. doi:10.1109/N-SSC.2006.4785858. S2CID 29759395. Archived from the original on July 13, 2007. Retrieved March 25, 2023.

- ^ Jorgenson, Dale W. (2000). Information Technology and the U.S. Economy: Presidential Address to the American Economic Association. American Economic Association. CiteSeerX 10.1.1.198.9555.

- ^ Jorgenson, Dale W.; Ho, Mun S.; Stiroh, Kevin J. (2008). "A Retrospective Look at the U.S. Productivity Growth Resurgence". Journal of Economic Perspectives. 22: 3–24. doi:10.1257/jep.22.1.3. hdl:10419/60598.

- ^ Grimm, Bruce T.; Moulton, Brent R.; Wasshausen, David B. (2002). "Information Processing Equipment and Software in the National Accounts" (PDF). U.S. Department of Commerce Bureau of Economic Analysis. Archived (PDF) from the original on October 9, 2022. Retrieved May 15, 2014.

- ^ "Nonfarm Business Sector: Real Output Per Hour of All Persons". Federal Reserve Bank of St. Louis Economic Data. 2014. Retrieved May 27, 2014.

- ^ Anderson, Richard G. (2007). "How Well Do Wages Follow Productivity Growth?" (PDF). Federal Reserve Bank of St. Louis Economic Synopses. Archived (PDF) from the original on October 9, 2022. Retrieved May 27, 2014.

- ^ Sandborn, Peter (April 2008). "Trapped on Technology's Trailing Edge". IEEE Spectrum. Retrieved November 27, 2011.

- ^ "Qualcomm Processor". Qualcomm. November 8, 2017.

- ^ Stokes, Jon (September 27, 2008). "Understanding Moore's Law". Ars Technica. Retrieved August 22, 2011.

- ^ Borkar, Shekhar; Chien, Andrew A. (May 2011). "The Future of Microprocessors". Communications of the ACM. 54 (5): 67. CiteSeerX 10.1.1.227.3582. doi:10.1145/1941487.1941507. S2CID 11032644. Retrieved November 27, 2011.

- ^ a b Bohr, Mark (January 2007). "A 30 Year Retrospective on Dennard's MOSFET Scaling Paper" (PDF). Solid-State Circuits Society. Archived (PDF) from the original on November 11, 2013. Retrieved January 23, 2014.

- ^ Esmaeilzedah, Hadi; Blem, Emily; St. Amant, Renee; Sankaralingam, Kartikeyan; Burger, Doug. "Dark Silicon and the end of multicore scaling" (PDF). Archived (PDF) from the original on October 9, 2022.

- ^ Hruska, Joel (February 1, 2012). "The death of CPU scaling: From one core to many – and why we're still stuck". ExtremeTech. Retrieved January 23, 2014.

- ^ Mistry, Kaizad (2011). "Tri-Gate Transistors: Enabling Moore's Law at 22nm and Beyond" (PDF). Intel Corporation at semiconwest.org. Archived from the original (PDF) on June 23, 2015. Retrieved May 27, 2014.

- ^ a b Hennessy, John L.; Patterson, David A. (June 4, 2018). "A New Golden Age for Computer Architecture: Domain-Specific Hardware/Software Co-Design, Enhanced Security, Open Instruction Sets, and Agile Chip Development" (PDF). International Symposium on Computer Architecture – ISCA 2018. Archived (PDF) from the original on October 9, 2022.

End of Growth of Single Program Speed?

- ^ a b "Private fixed investment, chained price index: Nonresidential: Equipment: Information processing equipment: Computers and peripheral equipment". Federal Reserve Bank of St. Louis. 2014. Retrieved May 12, 2014.

- ^ Nambiar, Raghunath; Poess, Meikel (2011). "Transaction Performance vs. Moore's Law: A Trend Analysis". Performance Evaluation, Measurement and Characterization of Complex Systems. Lecture Notes in Computer Science. Vol. 6417. Springer. pp. 110–120. doi:10.1007/978-3-642-18206-8_9. ISBN 978-3-642-18205-1. S2CID 31327565.

- ^ Feroli, Michael (2013). "US: is I.T. over?" (PDF). JPMorgan Chase Bank NA Economic Research. Archived (PDF) from the original on May 17, 2014. Retrieved May 15, 2014.

- ^ Byrne, David M.; Oliner, Stephen D.; Sichel, Daniel E. (March 2013). Is the Information Technology Revolution Over? (PDF). Finance and Economics Discussion Series Divisions of Research & Statistics and Monetary Affairs Federal Reserve Board. Washington, D.C.: Federal Reserve Board Finance and Economics Discussion Series (FEDS). Archived (PDF) from the original on June 9, 2014.

technical progress in the semiconductor industry has continued to proceed at a rapid pace ... Advances in semiconductor technology have driven down the constant-quality prices of MPUs and other chips at a rapid rate over the past several decades.

- ^ a b Aizcorbe, Ana; Oliner, Stephen D.; Sichel, Daniel E. (2006). "Shifting Trends in Semiconductor Prices and the Pace of Technological Progress". The Federal Reserve Board Finance and Economics Discussion Series. Retrieved May 15, 2014.

- ^ Aizcorbe, Ana (2005). "Why Are Semiconductor Price Indexes Falling So Fast? Industry Estimates and Implications for Productivity Measurement" (PDF). U.S. Department of Commerce Bureau of Economic Analysis. Archived from the original (PDF) on August 9, 2017. Retrieved May 15, 2014.

- ^ Sun, Liyang (April 25, 2014). "What We Are Paying for: A Quality Adjusted Price Index for Laptop Microprocessors". Wellesley College. Archived from the original on November 11, 2014. Retrieved November 7, 2014.

... compared with −25% to −35% per year over 2004–2010, the annual decline plateaus around −15% to −25% over 2010–2013.

- ^ Aizcorbe, Ana; Kortum, Samuel (2004). "Moore's Law and the Semiconductor Industry: A Vintage Model" (PDF). U.S. Department of Commerce Bureau of Economic Analysis. Archived (PDF) from the original on June 5, 2007. Retrieved May 27, 2014.

- ^ Markoff, John (2004). "Intel's Big Shift After Hitting Technical Wall". New York Times. Retrieved May 27, 2014.

- ^ Walter, Chip (July 25, 2005). "Kryder's Law". Scientific American. (Verlagsgruppe Georg von Holtzbrinck GmbH). Retrieved October 29, 2006.

- ^ Plumer, Martin L.; et al. (March 2011). "New Paradigms in Magnetic Recording". Physics in Canada. 67 (1): 25–29. arXiv:1201.5543. Bibcode:2012arXiv1201.5543P.

- ^ Mellor, Chris (November 10, 2014). "Kryder's law craps out: Race to UBER-CHEAP STORAGE is OVER". theregister.co.uk. UK: The Register. Retrieved November 12, 2014.

Currently 2.5-inch drives are at 500GB/platter with some at 600GB or even 667GB/platter – a long way from 20TB/platter. To reach 20TB by 2020, the 500GB/platter drives will have to increase areal density 44 times in six years. It isn't going to happen. ... Rosenthal writes: "The technical difficulties of migrating from PMR to HAMR, meant that already in 2010 the Kryder rate had slowed significantly and was not expected to return to its trend in the near future. The floods reinforced this."

- ^ Hecht, Jeff (2016). "Is Keck's Law Coming to an End? – IEEE Spectrum". IEEE. Retrieved June 16, 2023.

- ^ "Gerald Butters is a communications industry veteran". Forbes.com. Archived from the original on October 12, 2007.

- ^ "Board of Directors". LAMBDA OpticalSystems. Retrieved August 22, 2011.

- ^ Tehrani, Rich. "As We May Communicate". Tmcnet.com. Retrieved August 22, 2011.

- ^ Robinson, Gail (September 26, 2000). "Speeding net traffic with tiny mirrors". EE Times. Archived from the original on January 7, 2010. Retrieved August 22, 2011.

- ^ Nielsen, Jakob (April 5, 1998). "Nielsen's Law of Internet Bandwidth". Alertbox. Retrieved August 22, 2011.

- ^ Switkowski, Ziggy (April 9, 2009). "Trust the power of technology". The Australian. Retrieved December 2, 2013.

- ^ Sirer, Emin Gün; Farrow, Rik. Some Lesser-Known Laws of Computer Science (PDF). Archived (PDF) from the original on October 9, 2022. Retrieved December 2, 2013.

- ^ "Using Moore's Law to Predict Future Memory Trends". November 21, 2011. Retrieved December 2, 2013.

- ^ Myhrvold, Nathan (June 7, 2006). "Moore's Law Corollary: Pixel Power". The New York Times. Retrieved November 27, 2011.

- ^ Kennedy, Randall C. (April 14, 2008). "Fat, fatter, fattest: Microsoft's kings of bloat". InfoWorld. Retrieved August 22, 2011.

- ^ Rider, Fremont (1944). The Scholar and the Future of the Research Library. Hadham Press. OCLC 578215272.

- ^ Life 2.0. (August 31, 2006). The Economist

- ^ Carlson, Robert H. (2010). Biology Is Technology: The Promise, Peril, and New Business of Engineering Life. Harvard University Press. ISBN 978-0-674-05362-5.

- ^ Carlson, Robert H. (September 2003). "The Pace and Proliferation of Biological Technologies". Biosecurity and Bioterrorism: Biodefense Strategy, Practice, and Science. 1 (3): 203–214. doi:10.1089/153871303769201851. PMID 15040198. S2CID 18913248.

- ^ Ebbinghaus, Hermann (1913). Memory: A Contribution to Experimental Psychology. Columbia University. p. 42, Figure 2. ISBN 9780722229286.

- ^ Hall, Granville Stanley; Titchene, Edward Bradford (1903). "The American Journal of Psychology".

- ^ Wright, T. P. (1936). "Factors Affecting the Cost of Airplanes". Journal of the Aeronautical Sciences. 3 (4): 122–128. doi:10.2514/8.155.

- ^ Cherry, Steven (2004). "Edholm's law of bandwidth". IEEE Spectrum. 41 (7): 58–60. doi:10.1109/MSPEC.2004.1309810. S2CID 27580722.

- ^ Jindal, R. P. (2009). "From millibits to terabits per second and beyond - over 60 years of innovation". 2009 2nd International Workshop on Electron Devices and Semiconductor Technology. pp. 1–6. doi:10.1109/EDST.2009.5166093. ISBN 978-1-4244-3831-0. S2CID 25112828.

Further reading

[edit]- Brock, David C., ed. (2006). Understanding Moore's Law: Four Decades of Innovation. Philadelphia: Chemical Heritage Foundation. ISBN 0-941901-41-6. OCLC 66463488.

- Mody, Cyrus (2016). The Long Arm of Moore's law: Microelectronics and American Science. Cambridge, Massachusetts: Massachusetts Institute of Technology Press. ISBN 978-0262035491.

- Thackray, Arnold; Brock, David C.; Jones, Rachel (2015). Moore's Law: The Life of Gordon Moore, Silicon Valley's Quiet Revolutionary. New York: Basic Books. ISBN 978-0-465-05564-7. OCLC 0465055648.

- Tuomi, Ilkka (November 2002). "The Lives and Death of Moore's Law". First Monday. 7 (11). doi:10.5210/fm.v7i11.1000.

External links

[edit]- Intel press kit – released for Moore's Law's 40th anniversary, with a 1965 sketch by Moore

- No Technology has been more disruptive... Slide show of microchip growth

- Intel (IA-32) CPU speeds 1994–2005 – speed increases in recent years have seemed to slow with regard to percentage increase per year (available in PDF or PNG format)

- International Technology Roadmap for Semiconductors (ITRS)

- A C|net FAQ about Moore's Law at archive.today (archived 2013-01-02)

- ASML's 'Our Stories', Gordon Moore about Moore's Law, ASML Holding

- "Why Moore's Law Matters". Asianometry. March 2023 – via YouTube.

- Moore’s Law at Intel